TLine3

Lossless transmission line with characteristic impedance Z0 and frequency F

![]()

Library

Electrical/Analog/Lines

Description

Lossless transmission line with characteristic impedance Z0 and frequency F The lossless transmission line TLine3 is a two Port. Both port branches consist of a resistor with value of the characteristic impedance Z0 and a controlled voltage source that takes into consideration the transmission delay. For further details see Branin's article below. Resistance R' and conductance C' per meter are assumed to be zero. The characteristic impedance Z0 can be derived from inductance and capacitance per length (L' resp. C'), i. e. Z0 = sqrt(L'/C'). The length of the line is equal to a quarter of the wavelength corresponding to the frequency F, i. e. the transmission delay is the quotient of 4 and F. In this case, the characteristic impedance is called natural impedance.

References:

- Branin Jr., F. H.

- Transient Analysis of Lossless Transmission Lines. Proceedings of the IEEE 55(1967), 2012 - 2013

- Hoefer, E. E. E.; Nielinger, H.

- SPICE : Analyseprogramm fuer elektronische Schaltungen. Springer-Verlag, Berlin, Heidelberg, New York, Tokyo, 1985.

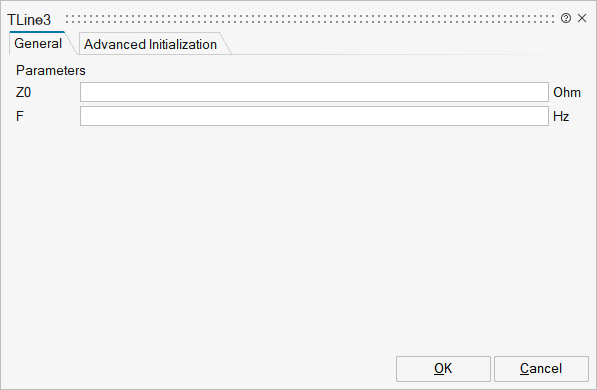

Parameters

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_Z0 | Z0 | Natural impedance | Scalar | |

mo_F | F | Frequency | Scalar | |

mo_TD | TD | Scalar |

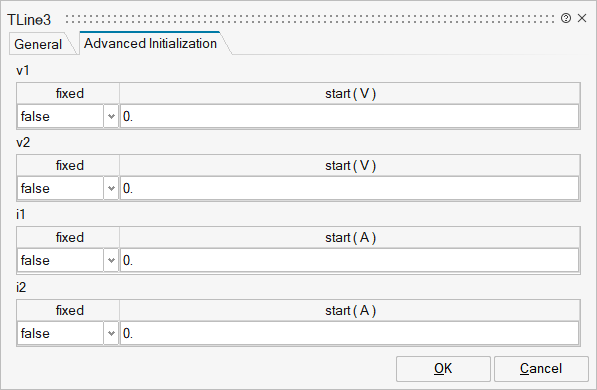

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_v1 | v1 | v1 | Structure | |

mo_v1/fixed | fixed | Cell of scalars | true | |

mo_v1/start | start | Cell of scalars | ||

mo_v2 | v2 | v2 | Structure | |

mo_v2/fixed | fixed | Cell of scalars | true | |

mo_v2/start | start | Cell of scalars | ||

mo_i1 | i1 | i1 | Structure | |

mo_i1/fixed | fixed | Cell of scalars | true | |

mo_i1/start | start | Cell of scalars | ||

mo_i2 | i2 | i2 | Structure | |

mo_i2/fixed | fixed | Cell of scalars | true | |

mo_i2/start | start | Cell of scalars |

Ports

| Name | Type | Description | IO Type | Number |

|---|---|---|---|---|

p1 | implicit | Positive electrical pin of port 1 | input | 1 |

n1 | implicit | Negative electrical pin of port 1 | output | 1 |

p2 | implicit | Positive electrical pin of port 2 | input | 2 |

n2 | implicit | Negative electrical pin of port 2 | output | 2 |