INV3SL

Tristate inverter with enable active low

![]()

Library

Electrical/Digital/Tristates

Description

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

and for tristate table http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_misc.vhd

Truth Table

| DataIn | Enable | DataOut* |

| * | U | U |

| * | X | UX |

| * | 0 | Not DataIn |

| * | 1 | Z |

| * | Z | UX |

| * | W | UX |

| * | L | Not DataIn |

| * | H | Z |

| * | - | UX |

UX: if dataIn == U then U else X DataOut*: Strength map for DataOut according to tristate table Buf3slTable

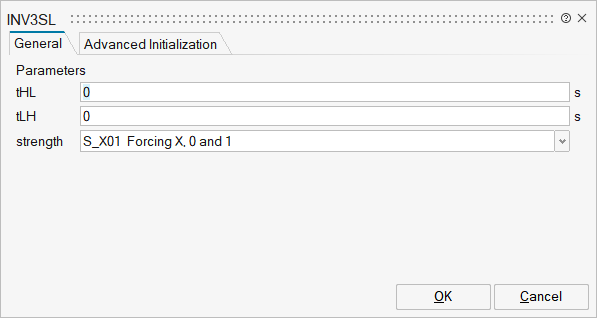

Parameters

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_tHL | tHL | High->Low delay | Scalar | |

mo_tLH | tLH | Low->High delay | Scalar | |

mo_strength | strength | output strength | Structure | |

mo_strength/choice1 | S_X01 Forcing X, 0 and 1 | Number | 0 | |

mo_strength/choice2 | S_X0H Forcing X, 0 and Weak 1 | Number | 0 | |

mo_strength/choice3 | S_XL1 Forcing X, 1 and Weak 0 | Number | 0 | |

mo_strength/choice4 | S_X0Z Forcing X, 0 and High Impedance | Number | 0 | |

mo_strength/choice5 | S_XZ1 Forcing X, 1 and High Impedance | Number | 0 | |

mo_strength/choice6 | S_WLH Weak X, 0 and 1 | Number | 0 | |

mo_strength/choice7 | S_WLZ Weak X, 0 and High Impedance | Number | 0 | |

mo_strength/choice8 | S_WZH Weak X, 1 and High Impedance | Number | 0 | |

mo_strength/choice9 | S_W0H Weak X, 1 and Forcing 0 | Number | 0 | |

mo_strength/choice10 | S_WL1 Weak X, 0 and Forcing 1 | Number | 0 |

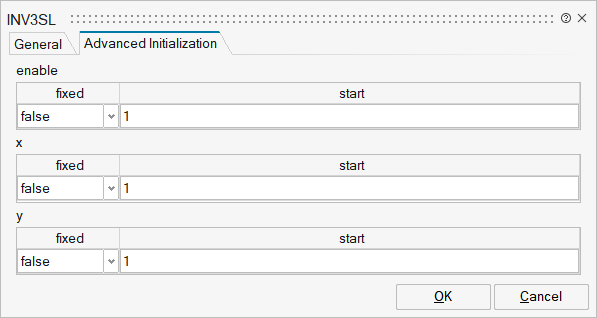

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_enable | enable | enable | Structure | |

mo_enable/fixed | fixed | Cell of scalars | true | |

mo_enable/start | start | Cell of scalars | ||

mo_x | x | x | Structure | |

mo_x/fixed | fixed | Cell of scalars | true | |

mo_x/start | start | Cell of scalars | ||

mo_y | y | y | Structure | |

mo_y/fixed | fixed | Cell of scalars | true | |

mo_y/start | start | Cell of scalars |

Ports

| Name | Type | Description | IO Type | Number |

|---|---|---|---|---|

enable | implicit | input | 1 | |

x | implicit | input | 2 | |

y | implicit | output | 1 |