Package Modelica.Electrical.Digital.Tristates

Package Modelica.Electrical.Digital.TristatesTransfergates, Buffers, Inverters, and WiredX

Package Modelica.Electrical.Digital.Tristates

Package Modelica.Electrical.Digital.Tristates

Standard package icon.

Extends from Modelica.Icons.Package (Icon for standard packages).

| Name | Description |

|---|---|

BUF3S | Tristate buffer with enable active high |

BUF3SL | Tristate buffer with enable active low |

INV3S | Tristate Inverter with enable active high |

INV3SL | Tristate inverter with enable active low |

NRXFERGATE | Transfergate with enable active high. Output strength reduced. |

NXFERGATE | Transfergate with enable active high |

PRXFERGATE | Transfergate with enable active low. Output strength reduced. |

PXFERGATE | Transfergate with enable active low |

WiredX | Wired node with multiple input and one output |

Model Modelica.Electrical.Digital.Tristates.NXFERGATE

Model Modelica.Electrical.Digital.Tristates.NXFERGATE

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

Truth Table

| DataIn | Enable | DataOut |

| * | U | U |

| * | X | UX |

| * | 0 | Z |

| * | 1 | DataIn |

| * | Z | UX |

| * | W | UX |

| * | L | Z |

| * | H | DataIn |

| * | - | UX |

UX: if dataIn == U then U else X

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

| Type | Name | Description |

|---|---|---|

input DigitalInput | enable | |

input DigitalInput | x | |

output DigitalOutput | y |

Model Modelica.Electrical.Digital.Tristates.NRXFERGATE

Model Modelica.Electrical.Digital.Tristates.NRXFERGATE

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

Truth Table

| DataIn | Enable | DataOut |

| * | U | U |

| * | X | UW |

| * | 0 | Z |

| * | 1 | DataIn, Strength Reduced |

| * | Z | UW |

| * | W | UW |

| * | L | Z |

| * | H | DataIn, Strength Reduced |

| * | - | UW |

UW: if dataIn == U then U else W Strength Reduced: 0 -> L, 1 -> H, X -> W

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

| Type | Name | Description |

|---|---|---|

input DigitalInput | enable | |

input DigitalInput | x | |

output DigitalOutput | y |

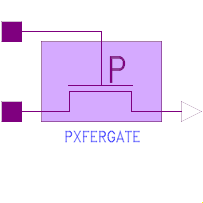

Model Modelica.Electrical.Digital.Tristates.PXFERGATE

Model Modelica.Electrical.Digital.Tristates.PXFERGATE

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

Truth Table

| DataIn | Enable | DataOut |

| * | U | U |

| * | X | UX |

| * | 0 | DataIn |

| * | 1 | Z |

| * | Z | UX |

| * | W | UX |

| * | L | DataIn |

| * | H | Z |

| * | - | UX |

UX: if dataIn == U then U else X

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

| Type | Name | Description |

|---|---|---|

input DigitalInput | enable | |

input DigitalInput | x | |

output DigitalOutput | y |

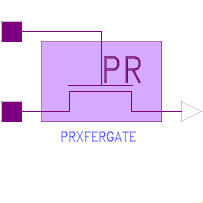

Model Modelica.Electrical.Digital.Tristates.PRXFERGATE

Model Modelica.Electrical.Digital.Tristates.PRXFERGATE

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

Truth Table

| DataIn | Enable | DataOut |

| * | U | U |

| * | X | UW |

| * | 0 | DataIn, Strength Reduced |

| * | 1 | Z |

| * | Z | UW |

| * | W | UW |

| * | L | DataIn, Strength Reduced |

| * | H | Z |

| * | - | UW |

UW: if dataIn == U then U else W Strength Reduced: 0 -> L, 1 -> H, X -> W

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

| Type | Name | Description |

|---|---|---|

input DigitalInput | enable | |

input DigitalInput | x | |

output DigitalOutput | y |

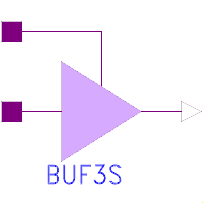

Model Modelica.Electrical.Digital.Tristates.BUF3S

Model Modelica.Electrical.Digital.Tristates.BUF3S

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

and for tristate table http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_misc.vhd

Truth Table

| DataIn | Enable | DataOut* |

| * | U | U |

| * | X | UX |

| * | 0 | Z |

| * | 1 | DataIn |

| * | Z | UX |

| * | W | UX |

| * | L | Z |

| * | H | DataIn |

| * | - | UX |

UX: if dataIn == U then U else X DataOut*: Strength map for DataOut according to tristate table Buf3sTable

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

Strength | strength | S.'S_X01' | output strength |

| Type | Name | Description |

|---|---|---|

input DigitalInput | enable | |

input DigitalInput | x | |

output DigitalOutput | y |

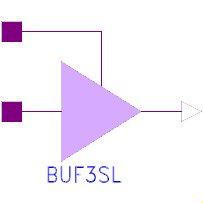

Model Modelica.Electrical.Digital.Tristates.BUF3SL

Model Modelica.Electrical.Digital.Tristates.BUF3SL

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

and for tristate table http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_misc.vhd

Truth Table

| DataIn | Enable | DataOut* |

| * | U | U |

| * | X | UX |

| * | 0 | DataIn |

| * | 1 | Z |

| * | Z | UX |

| * | W | UX |

| * | L | DataIn |

| * | H | Z |

| * | - | UX |

UX: if dataIn == U then U else X DataOut*: Strength map for DataOut according to tristate table Buf3slTable

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

Strength | strength | S.'S_X01' | output strength |

| Type | Name | Description |

|---|---|---|

input DigitalInput | enable | |

input DigitalInput | x | |

output DigitalOutput | y |

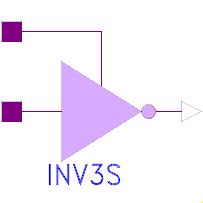

Model Modelica.Electrical.Digital.Tristates.INV3S

Model Modelica.Electrical.Digital.Tristates.INV3S

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

and for tristate table http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_misc.vhd

Truth Table

| DataIn | Enable | DataOut* |

| * | U | U |

| * | X | UX |

| * | 0 | Z |

| * | 1 | Not DataIn |

| * | Z | UX |

| * | W | UX |

| * | L | Z |

| * | H | Not DataIn |

| * | - | UX |

UX: if dataIn == U then U else X DataOut*: Strength map for DataOut according to tristate table Buf3sTable

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

Strength | strength | S.'S_X01' | output strength |

| Type | Name | Description |

|---|---|---|

input DigitalInput | enable | |

input DigitalInput | x | |

output DigitalOutput | y |

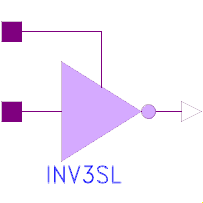

Model Modelica.Electrical.Digital.Tristates.INV3SL

Model Modelica.Electrical.Digital.Tristates.INV3SL

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

and for tristate table http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_misc.vhd

Truth Table

| DataIn | Enable | DataOut* |

| * | U | U |

| * | X | UX |

| * | 0 | Not DataIn |

| * | 1 | Z |

| * | Z | UX |

| * | W | UX |

| * | L | Not DataIn |

| * | H | Z |

| * | - | UX |

UX: if dataIn == U then U else X DataOut*: Strength map for DataOut according to tristate table Buf3slTable

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

Strength | strength | S.'S_X01' | output strength |

| Type | Name | Description |

|---|---|---|

input DigitalInput | enable | |

input DigitalInput | x | |

output DigitalOutput | y |

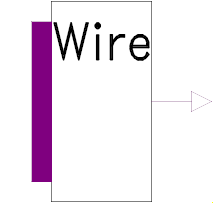

Model Modelica.Electrical.Digital.Tristates.WiredX

Model Modelica.Electrical.Digital.Tristates.WiredX

Wires n input signals in one output signal, without delay.

Resolution table is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_misc.vhd

Extends from Modelica.Electrical.Digital.Interfaces.MISO (Multiple input - single output).

| Type | Name | Default | Description |

|---|---|---|---|

Integer | n | 2 | Number of inputs |

| Type | Name | Description |

|---|---|---|

input DigitalInput | x[n] | Connector of Digital input signal vector |

output DigitalOutput | y | Connector of Digital output signal |