To configure the ADC, it’s a good idea to first insert an F28x Config block in your diagram and set the CPU to your device.

Oversamling the ADC results in a reduction of noise. For every four oversamples, you’ll see one additional bit of precision. Examples of how to oversample an ADC channel, see Examples > Embedded > Piccolo > ADC.

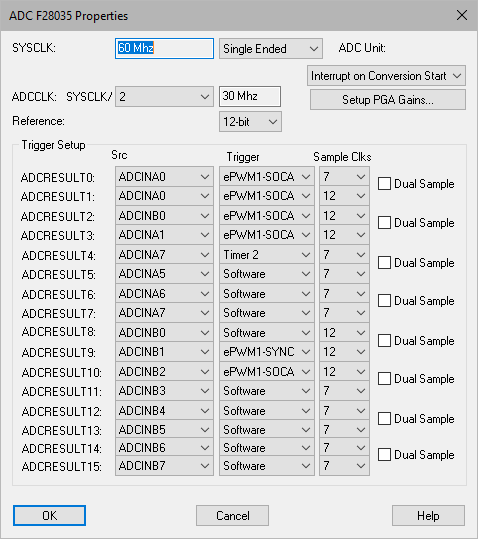

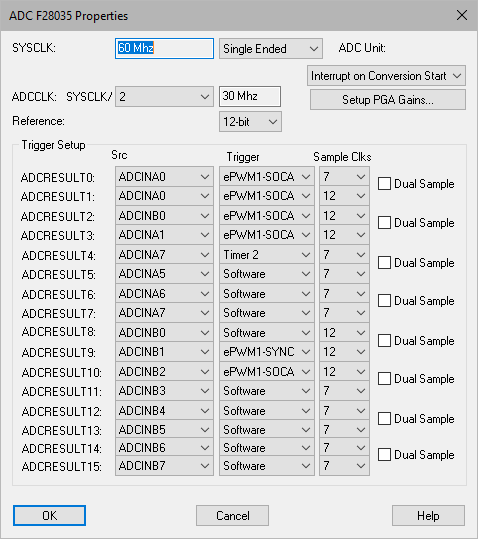

Note: The ADC Config dialog box is dependent on the target you select. If you selected an older device, the dialog box parameters are different from the ones shown below.

12-bit/16-bit: Specifies either a 12-bit or 16-bit analog measurement. This parameter is available on newer Piccolo chips.

ADCCLK: Specifies the analog-to-digital converter clock.

ADC Unit: Specifies the ADC unit to be configured. This parameter is available on newer Piccolo chips.

Dual Sample: If a dual sampling is selected, two consecutive SOCs (SOCx and SOC(x+1) or ADCRESULTx and ADCRESULTx+1) are used. The even numbered ADCRESULT contains the ADCINAy value while the next (odd numbered) ADCRESULT contains the corresponding ADCINBy value. Only these ADC inputs can be dual sampled. On clicking the dual sample, the even numbered ADCRESULT Src field must contain only the ADCINA0 to ADCINA7. Once the ADCINAy value is selected, the next odd numbered ADCRESULR Src field must contain the ADCINBy ONLY with the selection fixed. This parameter is available on Piccolo, F2802x, F2803x, F2805x, F2806x, and Concerto.

Interrupt on Conversion End: Generates interrupt on conversion end.

Interrupt on Conversion Start: Generates interrupt on conversion start.

Reference: Specifies the voltage reference. This parameter is available on Piccolo, F2802x, F2803x, F2805x, F2806x, and Concerto chips.

Setup PGA Gains: Invokes a dialog box to set the gain mode and output filter resistance for all PGAs.

Single Ended/Differential: When you choose Single Ended, Embed compares a single channel relative to analog ground. When you choose Differential, Embed measures the voltage difference between pairs of channels. This parameter is available on newer Piccolo chips.

SYSCLK: Indicates the speed of the CPU clock.

Dual Sample: Lets you sample pairs of channels simultaneously. This parameter is available for targets that do not have multiple ADC units.

Sample Clks: Specifies the sample and hold duration in units of system clocks.

Src: Specifies the analog pin on which to measure the voltage.

Trigger: Specifies the signal that will trigger a conversion.